Contacts : A. Ouerghi (CNRS-LPN), R. Belkhou (synchrotron SOLEIL) et A. Barbier (CEA)

A. Ouerghi (LPN-CNRS), M. Marangolo et M. Eddrief (INSP-Paris 6),

R. Belkhou, S. El Moussaoui, F. Sirotti, M. Silly (Synchrotron SOLEIL),

M. Portail (CRHEA-CNRS), A. Barbier et D. Martinotti(IRAMIS/SPCSI)

Une étude multi-technique (LEEM*, LEED**, STM***) réalisée par une collaboration entre les équipes du LPN-Marcoussis, du synchrotron Soleil et du SPCSI, a permis de caractériser une nouvelle méthode d'élaboration de couches de graphène. Les couches sont obtenues sur des films minces de SiC déposés sur des substrats de silicium standards pour la microélectronique. Cette convergence entre une nouvelle technologie graphène et la technologie silicium est un pas vers la réalisation de composants électroniques de haute performance.

* LEEM : Low Energy Electron Microscopy (Microscopie à électrons lents)

**LEED : Low Energy Electron Diffraction (Diffractions d'électrons lents)

***STM : Scanning Tunneling Microscope (Microscope à effet tunnel)

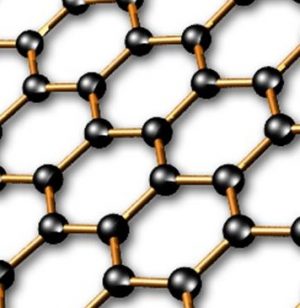

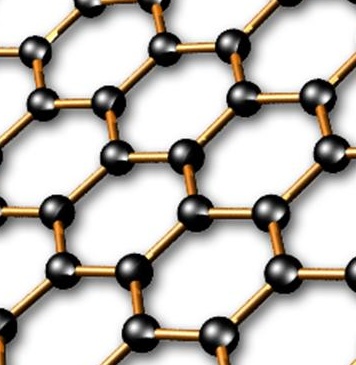

Le graphène est un cristal bidimensionnel (monoplan) de carbone dont l'empilement constitue le graphite. Isolé pour la première fois en 2004 par Andre Geim, du Département de Physique de l'Université de Manchester, qui a reçu pour cette découverte, conjointement avec Konstantin Novoselov, le prix Nobel de physique 2010. Le graphène suscite un engouement considérable à la fois dans la recherche académique et dans le monde industriel. Ce sont principalement les propriétés électroniques et de transports exceptionnels et uniques de ce matériau, dont la maîtrise reste un défi, qui expliquent cet intérêt mondial.

L’intérêt pour ce matériau repose tout d’abord sur les nouvelles perspectives d’applications technologiques, allant du stockage de charges électriques au guide d'onde. Pour les nanotechnologies, IBM Inc. dévoilait déjà en décembre dernier un premier prototype de transistor hyperfréquence à effet de champ basé sur la technologie graphène et opérant à plusieurs gigahertz. Récemment, le MIT-Boston présentait un multiplicateur de fréquence pouvant fonctionner à 300 Hz[2].

Ces applications de haute performance des couches de graphène sont directement liées :

– aux valeurs élevées de la mobilité des porteurs de charge qui avoisine 20 000 cm2/Vs, avec la particularité d’un transport balistique à température ambiante à l’échelle submicronique [1] ,

– à une conductivité thermique deux fois supérieure à celle du diamant (~ 5 000 W/mK),

– à son excellente stabilité chimique et thermique.

Cependant les propriétés exceptionnelles du graphène sont entièrement conditionnées par la qualité parfaite du matériau, qui demeure un challenge technologique.

A ce jour, deux voies d’élaboration sont connues. La première est l’exfoliation à partir de substrats massifs de graphite synthétique pyrolytique. Aisée à réaliser, cette méthode souffre d’un défaut majeur inhérent à la mosaïcité du substrat, très limitant pour les applications en microélectronique. La seconde méthode est basée sur la croissance épitaxiale de plans graphène sur des substrats de carbure de silicium. Cette méthode est à ce jour la plus prometteuse, malgré le coût de production très élevé des substrats SiC.

Le rapprochement des technologies silicium à celle du graphène faciliterait grandement le transfert industriel, la réduction des coûts de production et l’adaptation des chaines de production silicium au graphène. Dans ce sens, une nouvelle méthode d’élaboration basée sur des films minces de SiC déposés sur des substrats de silicium standard (4 pouces) a été développé récemment par nos équipes (collaboration CNRS (LPN), CEA et synchrotron SOLEIL). [3, 4]. L'étude est aussi orientée vers l'optimisation du procédé pour obtenir des couches de graphène de qualité uniforme sur des surfaces de grande taille.

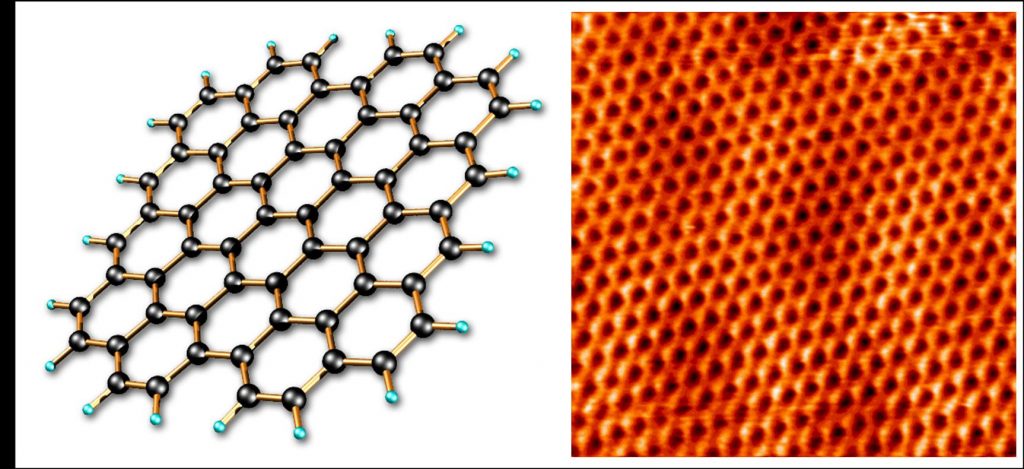

L’originalité de l'approche réside dans l’utilisation d’une couche d’accrochage SiC déposée sur des wafers de silicium, qui permet de s’affranchir d'un substrat SiC massif onéreux. La combinaison de méthodes de caractérisation structurale, microscopique et électronique (LEEM, LEED, STM, STS) montre que la couche SiC/Si possède des propriétés intrinsèques qui favorisent la formation de plans graphène d’une excellente qualité cristallographique (Figure 1). On peut estimer que cette méthode réduirait les coûts de production d'un facteur 10.

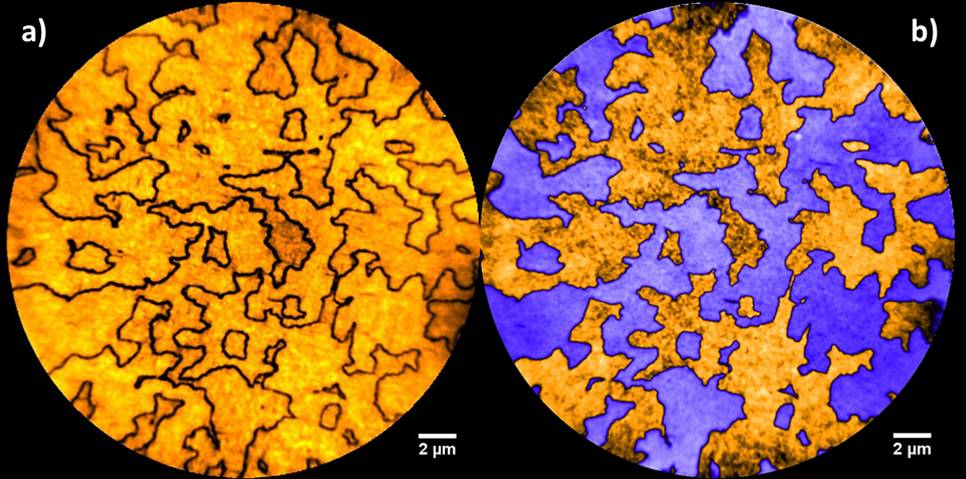

Pour étudier la morphologie, la cinétique de croissance et la structure des couches de graphène à l'échelle nanométrique, le microscope LEEM (Low Energy Electron Microscopy) de l'IRAMIS/SPCSI s'est révélé un outil de choix.. Cette technique a en effet permis l’identification et la caractérisation de la formation des couches monoatomiques de graphène et la détermination de la taille des domaines. Les résultats montrent l'excellente qualité des couches de graphène obtenues avec des tailles de domaines caractéristiques d'un ordre de grandeur supérieur à celles usuellement obtenues par les méthodes d’élaboration classique sur substrat massif SiC (Figure 2).

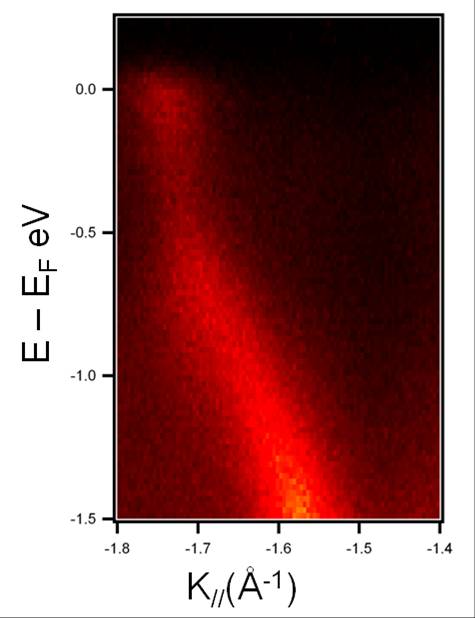

Ces études morphologiques ont été complétées par une caractérisation de la structure électronique d’une monocouche de graphène identifiée dans l'expérience LEEM au CEA, par STM, spectroscopie à effet Tunnel (STS) et STEM au LPN ainsi que par photoémissions résolue angulairement (ARPES [1]) au synchrotron SOLEIL sur la ligne TEMPO. L'étude ARPES montre au point K selon la direction GM la singularité de la densité d’états électroniques au niveau de Fermi dit « Cône de DIRAC » (Figure 3) signature de la qualité des couches de graphène en rapport avec leur haute conductivité bidimensionnelle.

Ces résultats prometteurs et encourageants, montrent que le graphène élaboré sur SiC/Si est une méthode applicable à l'élaboration de composants électroniques à base de carbone et de silicium. L’utilisation de substrat silicium pour la croissance du graphène devrait permettre d’adapter les méthodologies et la technologie silicium au graphène et de rendre possible une technologie d’électronique rapide moins couteuse et plus abordable industriellement.

Contacts :

1 Electric Field Effect in Atomically Thin Carbon Films, K. S. Novoselov, et al. Science 306, 666 (2004)

2 http://meetings.aps.org/Meeting/MAR09/Event/95805

3 Structural coherency of epitaxial graphene on 3C-SiC(111) epilayers on Si(111); A. Ouerghi, R. Belkhou, M. Marangolo, M. Silly, S. El Moussaoui, M. Eddrief, L.Largeau, M. Portail, and F. Sirotti, Appl. Phys. Lett. 97, 1 (2010)

4 Epitaxial graphene on 3C-SiC(111) pseudosubstrate: Structural and electronic properties; A. Ouerghi, M. Marangolo, R. Belkhou, S. El Moussaoui, M. G. Silly, M. Eddrief, L. Largeau, M. Portail, B. Fain, and F. Sirotti; Phys Rev B 82, 125445 (2010).

[1] ARPES : Angle Resolved PhotoEmission Spectroscopy