Circuit de réseau neuronal comprenant des nano synapses et des neurones CMOS

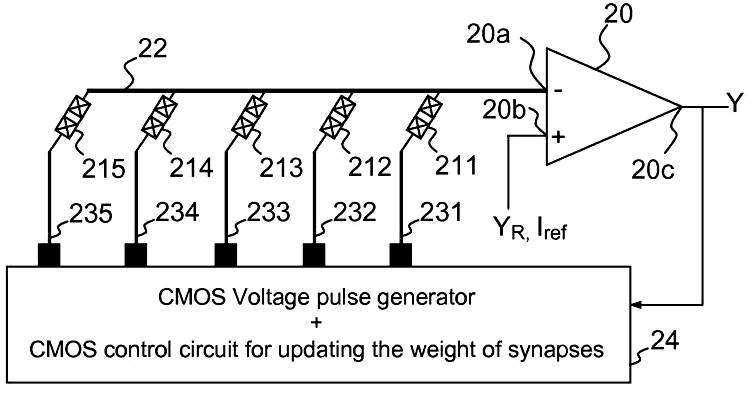

L'invention concerne un circuit de réseau neuronal comprenant des nano dispositifs (411-415, 421-425) jouant le rôle de synapses et des circuits CMOS (201, 202) jouant le rôle de neurones. Elle trouve une application toute particulière dans les circuits et systèmes de calcul faisant appel à des fonctions complexes ou traitant d'énormes quantités de données. Comparée à l'état de la technique, cette architecture promet une faible surface occupée, des vitesses élevées dues à un apprentissage hyperparallèle et une faible consommation. Les nano dispositifs (411-415, 421-425) comprennent deux bornes et sont reliés à des conducteurs en ligne (221, 222) et à des conducteurs en colonne (231-235) à la manière d'une matrice. Un circuit CMOS (201, 202) est relié à une extrémité de chaque conducteur en ligne (221, 222). Une caractéristique électrique entre les deux bornes de chaque nano dispositif (411-415, 421-425) est susceptible d'être modifiée par un signal appliqué à la deuxième borne. Le circuit de réseau neuronal comprend en outre, pour chaque conducteur en ligne (221, 222), des moyens (401, 402) conçus pour empêcher la modification des caractéristiques électriques des nano dispositifs (411-415, 421-425) reliés au conducteur en ligne (221, 222) correspondant par un signal appliqué à la deuxième borne de ces nano dispositifs.

Neural network circuit comprising nanoscale synapses and cmos neurons (WIPO link)

The invention relates to a neural network circuit comprising nanoscale devices (411-415, 421-425) acting as synapses and CMOS circuits (201, 202) acting as neurons. It finds a particular interest for computing circuits and systems involving complex functions or handling of huge amounts of data. Comparing with the existing proposals, this architecture promises small die area, high speed thanks to massively parallel learning and low power. The nanoscale devices (411-415, 421-425) comprise two terminals and are connected to row conductors (221, 222) and to column conductors (231-235) in a matrix-like fashion. A CMOS circuit (201, 202) is connected at one end of each row conductor (221, 222). An electrical characteristic between the two terminals of each nanoscale device (411-415, 421-425) is able to be modified by a signal applied to the second terminal. The neural network further comprises, for each row conductor (221, 222), means (401, 402) for preventing the electrical characteristics of the nanoscale devices (411-415, 421-425) connected to the considered row conductor (221, 222) from being modified by a signal applied to the second terminal of said nanoscale devices.