## Energy Efficient Embedded Non-Volatile Memory & Logic Based on Ferroelectric Hf(Zr)O<sub>2</sub>

3ɛFERRO is project for competitive, scalable FeRAM and logic-inmemory designs based on Si-compatible ferroelectric Hf<sub>x</sub>Zr<sub>1-x</sub>O<sub>2</sub>. The latest results on the materials optimization, logic design and integration into a 16 kbit test vehicle are highly encouraging.

### **Energy efficiency**

The 3εFERRO consortium is researching energy efficient non-volatile memory and logic devices based on Si-compatible ferroelectric HfZrO<sub>2</sub> (HZO) to provide advanced embedded solutions for normally-off microcontroller units used in IoT. The consortium is a balanced mix of large technology development laboratories and academia in partnership with ST Microelectronics to address the complex issues associated with materials optimization, circuit design, device fabrication and integration.

### July 2019 - Special session HfO<sub>2</sub>

Many fascinating presentations made in the joint ISAF-EMF-ICE special session on ferroelectric HfO<sub>2</sub>, Lausanne, July 2019. More details here:

http://lausanne2019.org/pages/special-sessionhfo2-based-ferroelectrics

# Negative capacitance stabilized

The ongoing debate on the reality of negative capacitance (NC) has, to a large extent, been resolved by the recent work of  $3\varepsilon$ FERRO partner NamLab who demonstrated that adding an additional dielectric layer (Ta<sub>2</sub>O<sub>5</sub>) stabilizes NC in ferroelectric HZO [*Nature* **464**, 565 (2019)]. The experiments were done in a capacitance geometry, suitable for memory storage.

Work at the Ecole Polytechnique Fédérale de Lausanne has demonstrated negative capacitance in a FeFET like geometry using a Si/SiO<sub>2</sub>/Si:HfO<sub>2</sub>/TiN structure. The NC shows up only at short (ns) pulses (and destroyed by dc). With faster pulses and thicker SiO<sub>2</sub> layers one can expect a stronger NC and lower level of leakage. Further enhancement of the NC may require more stable polarization without multidoman formation.

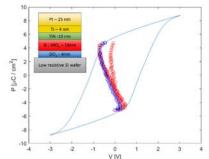

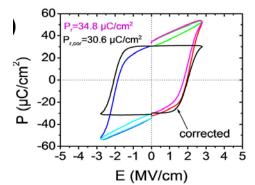

### Ferroelectric HZO on Ge

ignificant progress has been made on the growth of HZO on Ge substrates at the NCSRD in Athens for FeFET applications. At 225 °C, HZO crystallizes during deposition by molecular beam epitaxy and the ferroelectric orthorhombic phase is dominant.

Rapid thermal annealing (RTA) of the Ge/ HZO/TiN/Ti/Pt metal-ferroelectric-semiconductor stack at 500°C yields a record remanent polarization of 30.6 µC/cm<sup>2</sup> and an endurance of 10<sup>5</sup> cycles at 2.3 MV/cm.

The low T crystallization annealing is compatible with low boron dopant activation annealing in Ge. opening up interesting perspectives for an optimized "gate last" FeFET process flow. The results have been published in Appl. Phys. Lett. 114, 112901 (2019)

https://doi.org/10.1063/1.5090036

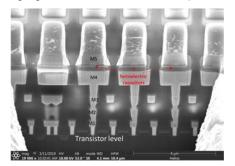

#### **BEOL HZO integration with** 130nm CMOS

he complete integration of FE lavers above CMOS devices (1T-1C MAD200 wafers): the full integration approach of sub-µm<sup>2</sup> HZObased capacitor was successfully achieved on a 16 kbit test vehicle produced at the CEA in Grenoble.

Wafers were processed by ST microelectronics with 130 nm node technology using the CEA MAD200v2 mask. After transistor fabrication, routing from M1 to M4 with standard process, bottom electrode was prepared at CEA. Wafers were then sent to NamLab for 10nm HZO growth and 10nm TiN capping. Following the specific cleaning procedure developed during the 1st year of the project, TiN top electrode was deposited in CEA. Then capacitors were patterned with DUV lithography. The capacitor size ranges from 300-550 nm diameter. The capacitors are encapsulated by silicon nitride and the process continues up to metal 5 (M5) level.

The figure shows a zoomed-out cross section of the 1T-1C full integration after M5 patterning. The first characterization results on the ferroelectric performance on the MAD200 test vehicle, originally designed for RRAM benchmarking are encouraging and full results will be reported soon.

### System benchmarking platform

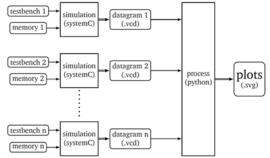

have realized benchmarking platform at the Ecole Centrale Lyon, metrics from simulations

а system-level taking performance

operated at the deviceand circuit-level.

The main evaluation tool is in SystemC, which enables direct interfacing to existing industry-standard benchmarks. This tool will guide design choices and provide quantified а feedback of the gains expected from normally-off computing and coarsegrain Logic-in-Memory (LiM).

"it is...possible to extrapolate these performance metrics to the system level"

Ian O'Connor (Ecole Centrale Lyon)

Having such a feedback also enables cooptimization at the device level, with parameters such as transistor footprints being guided from system-level performance considerations.

The architecture of the platform mimics a memory circuit, whose parts reproduce energy and latency metrics observed in smaller memory bitcell arrays. This enables the comparison of realistic workload performance under normally-off, coarse-grained LiM.